前置知识:Altium Designer 重拾指南 | 菜鸟救星 – 鸦鸦的巢穴 (crowya.com)

以下经验主要适用于开关电源等既有功率线又有信号线的场景。

多层板布局

以六层板为例,最外两层走功率,次外两层铺地,中间两层走信号。

功率线放在最外层,是因为散热好。

把信号线夹在地层中间,有利于屏蔽外部干扰。

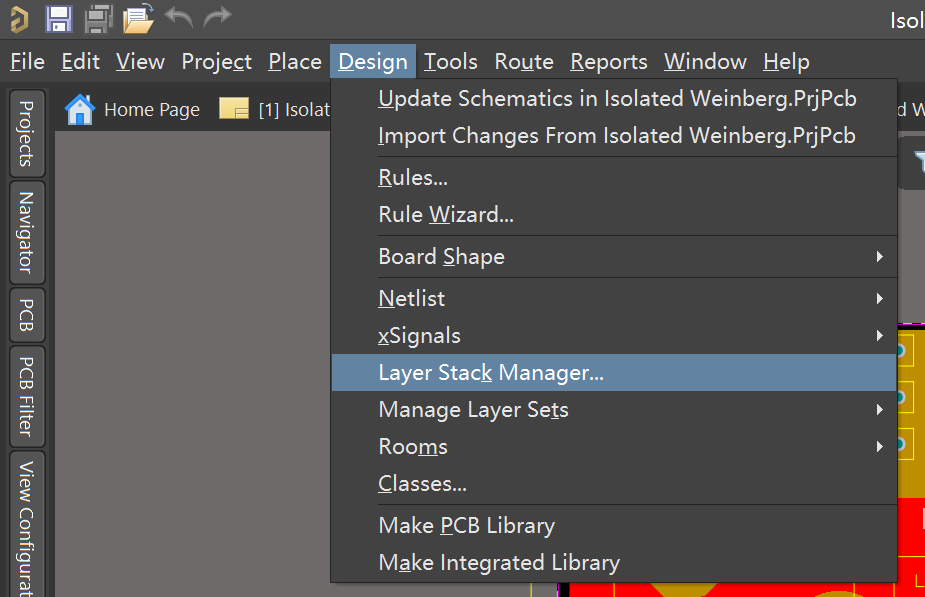

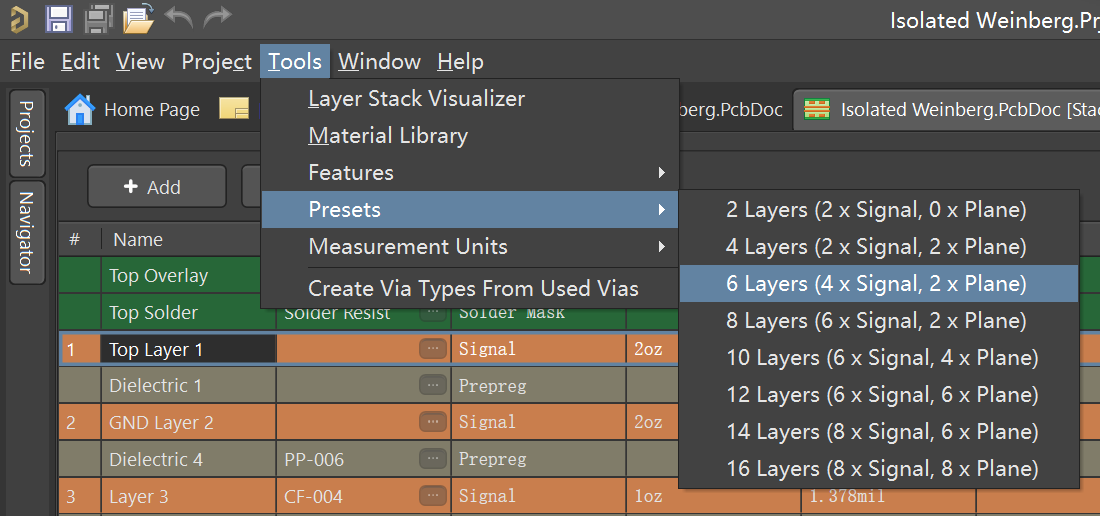

增加或减少层数是在菜单Design-Layer Stack Manager这里操作(快捷键DK)。

右键插入一个新的信号层。

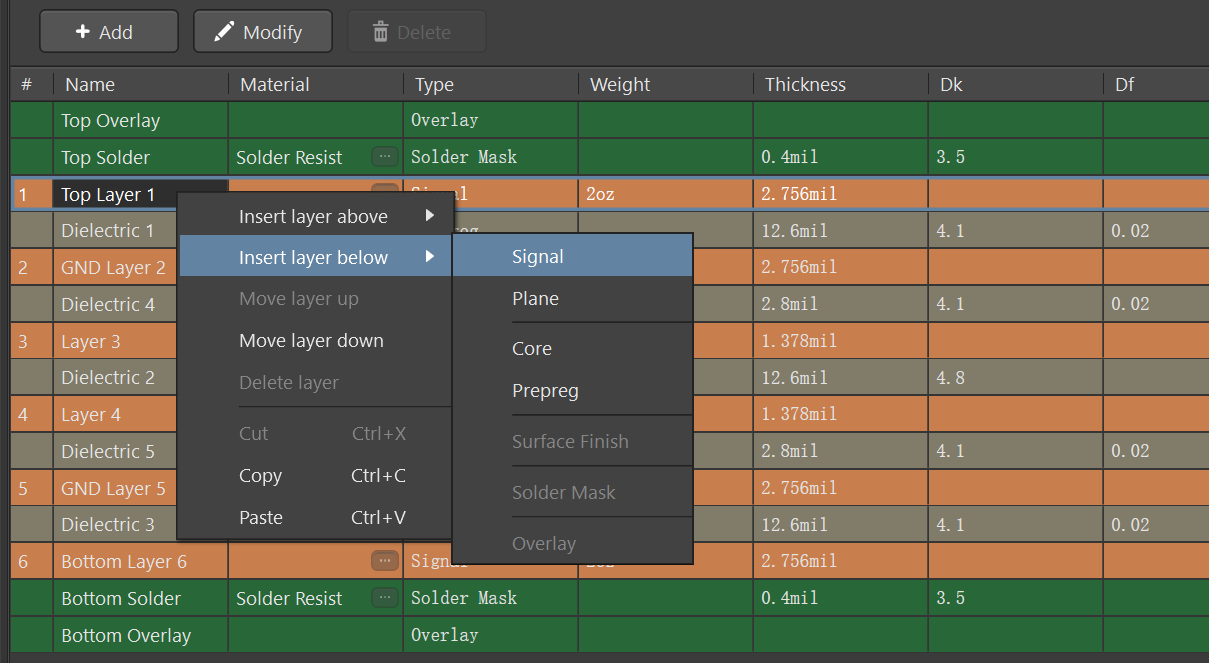

或者,用AD预设的六层板。

个人还是喜欢自己右键插入新板。

这里涉及到一个正片(Signal)和负片(Plane)的概念:

Signal就是走线的地方敷铜,Plane是默认敷铜,走线的地方挖空。

走线宽度

信号线一般10mil或者20mil就可以了,但是涉及驱动、电源的线要适当加粗,比如40mil、50mil[1]。

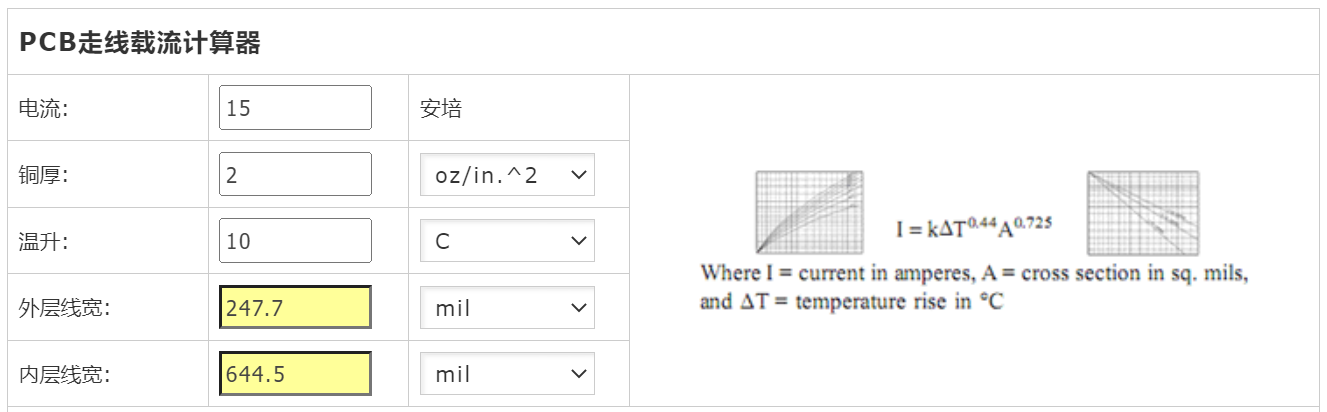

主功率的走线肯定要宽得多,可以用这个算:PCB走线载流计算器

以15A为例,可以看到所需的外层线宽比内层小得多,这也是为什么前面说最外层走功率。

一层线不够宽的话可以分两层走,比如顶层200mil,底层200mil,加起来就够了。

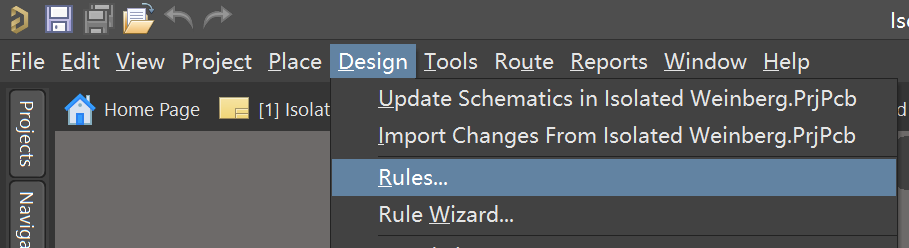

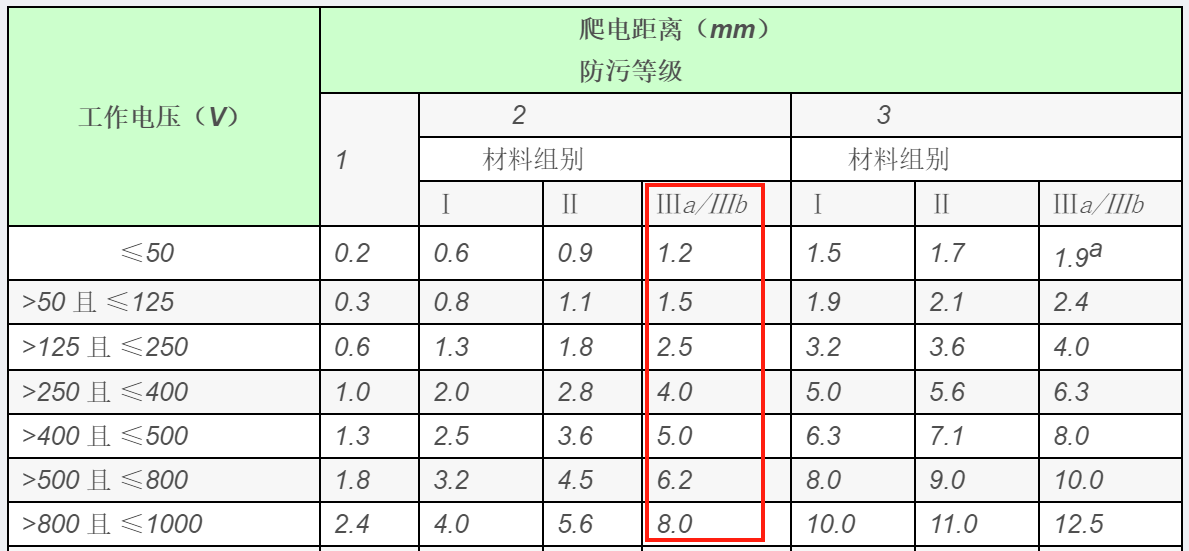

确定了宽度之后可以对功率线单独设置一个走线规则,在菜单Design-Rules这里(快捷键DR)。

网络类别(Class)的设置是在菜单Design-Classes这里(快捷键DC)。

需要注意的是每次从原理图更新PCB时不要把Class删掉。

驱动线、电源线同理。

绝缘间距

首先涉及到两个概念:

- 爬电距离:表面距离

- 电气间隙:空间距离

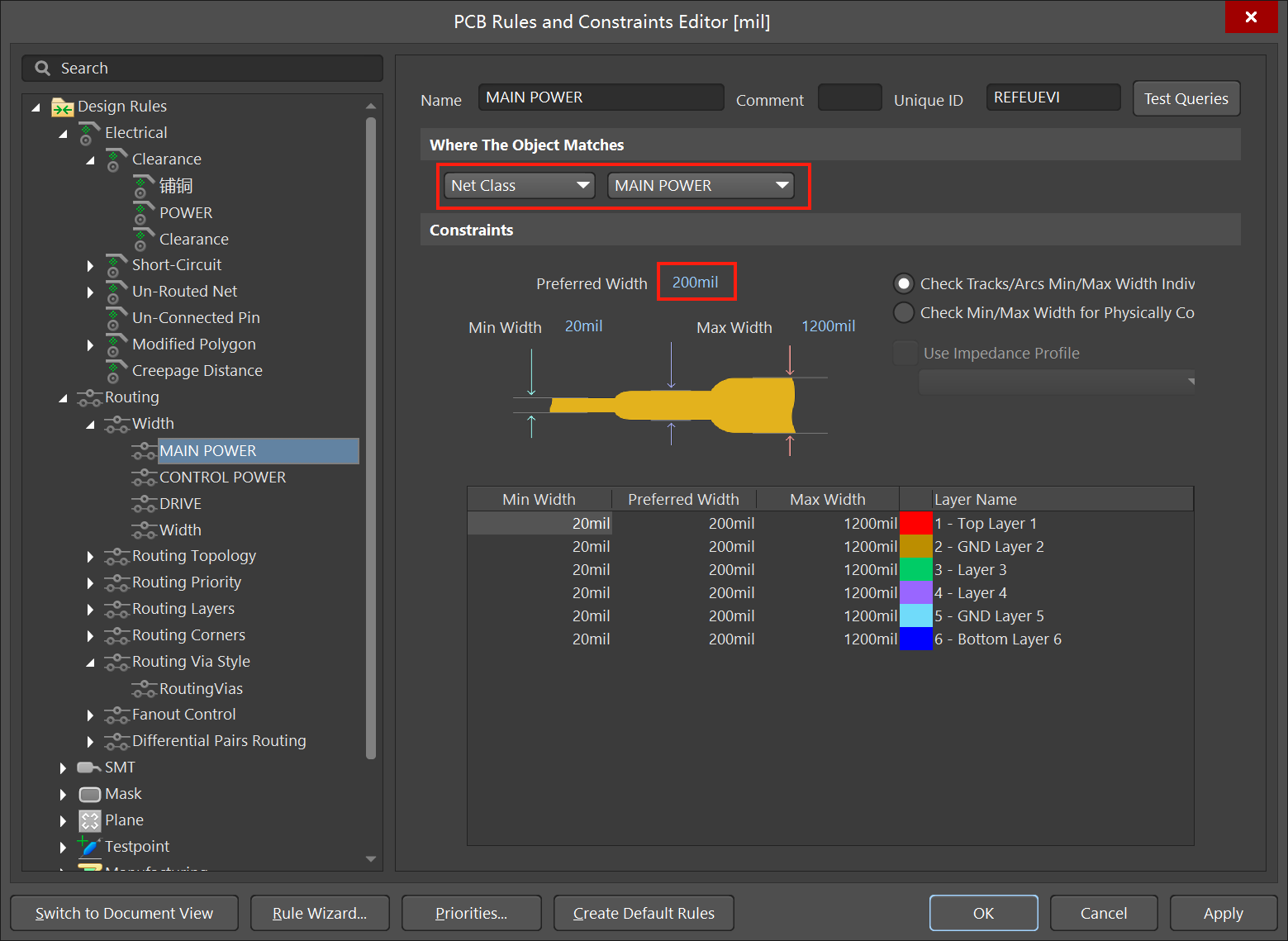

这个比较头大,标准比较杂乱捋不明白。我也不太清楚,就按污染等级2材料组别III来查表吧。

IEC60335-1:2001 表17-基本绝缘的最小爬电距离[2]

还有一种简单粗暴的说法是每100V按1mm来估算,300V大约3mm的样子。

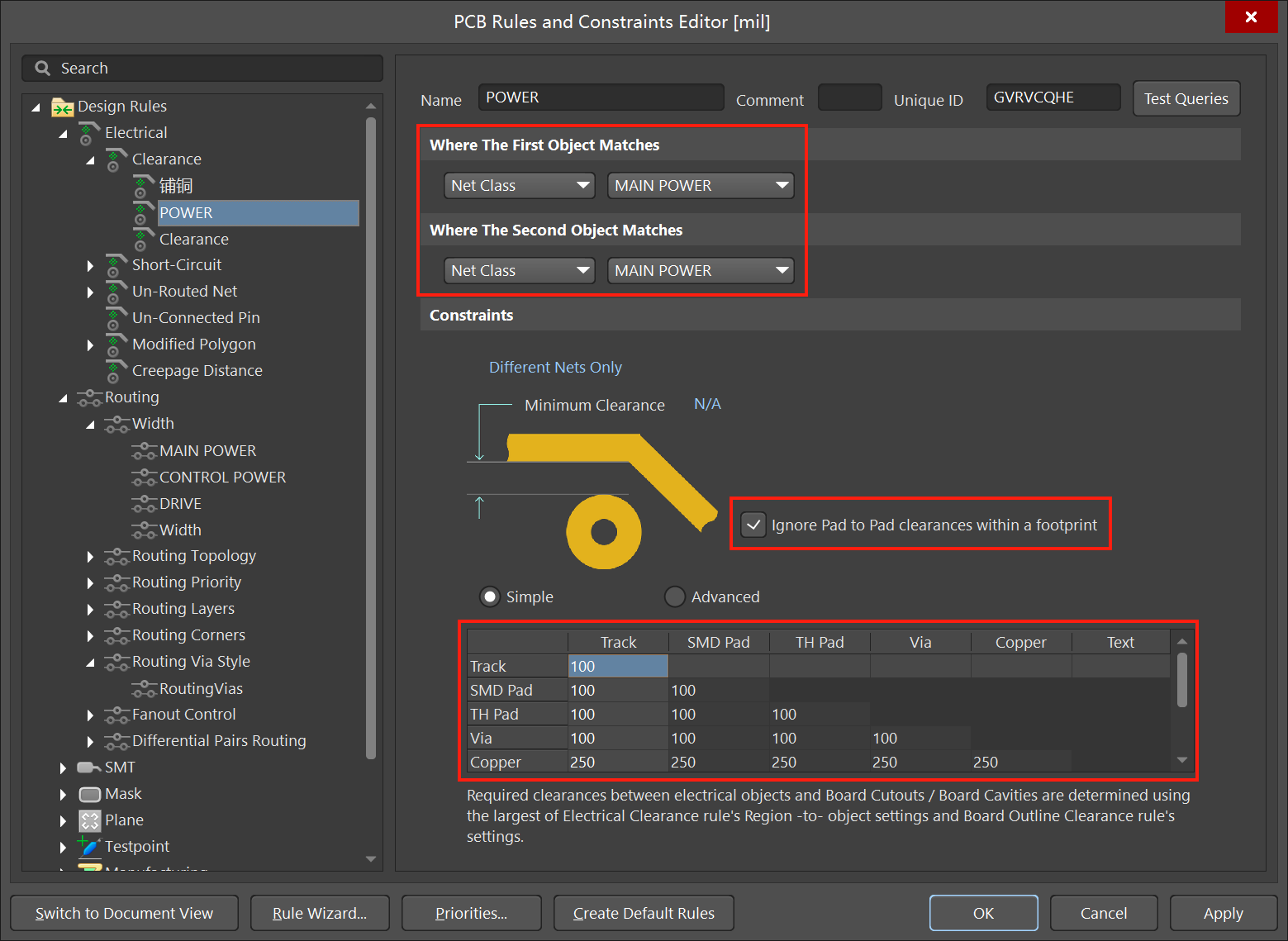

确定了绝缘间距之后就可以为功率线设置一个专属的规则了,同样是在菜单Design-Rules这里(快捷键DR)。

100mil=2.54mm

250mil=6.35mm

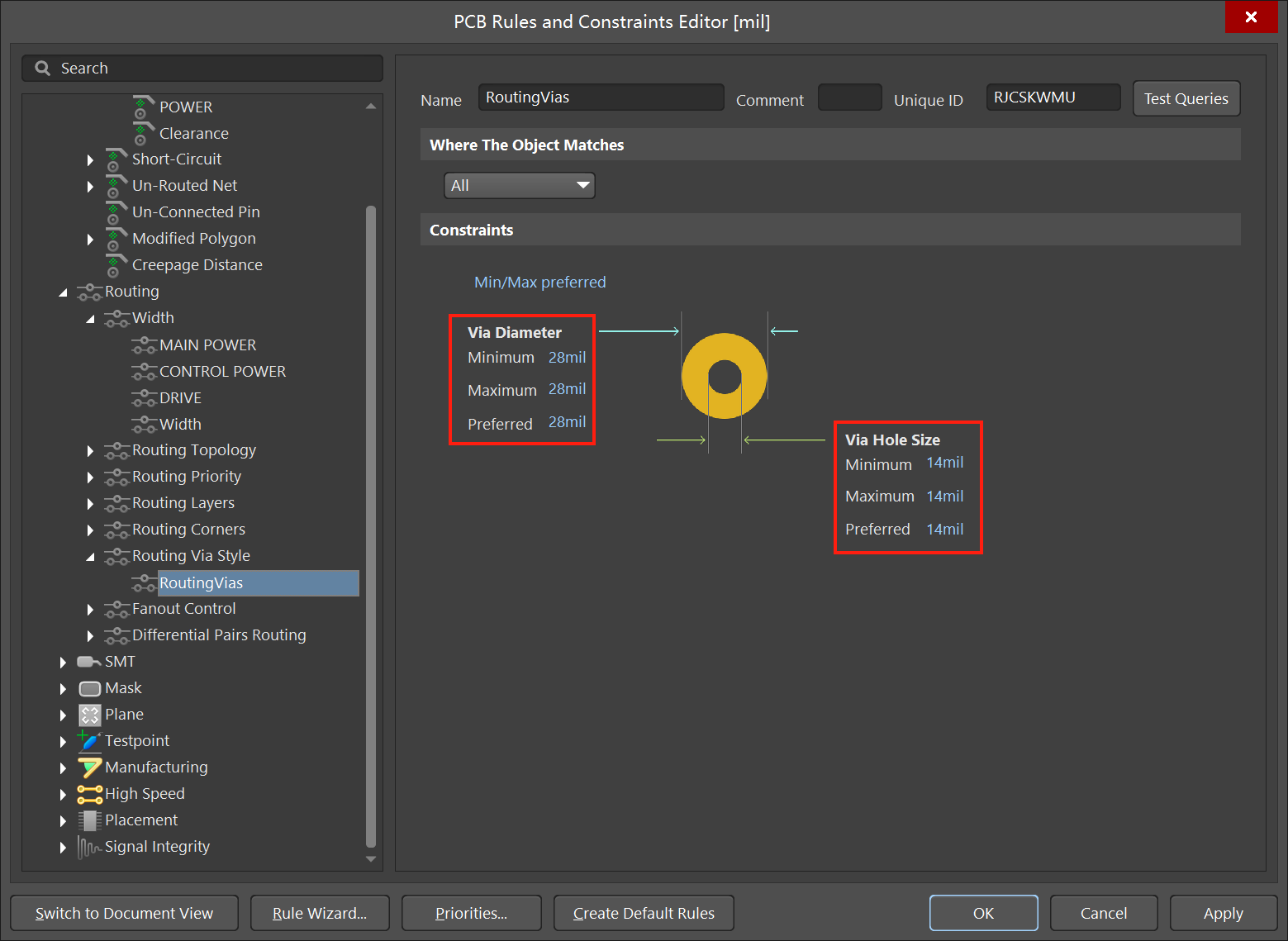

过孔直径

还是在菜单Design-Rules这里(快捷键DR)。

一般都是通孔,直径差不多就可以了,大点小点问题不大,比如我这里外径28mil内径14mil。

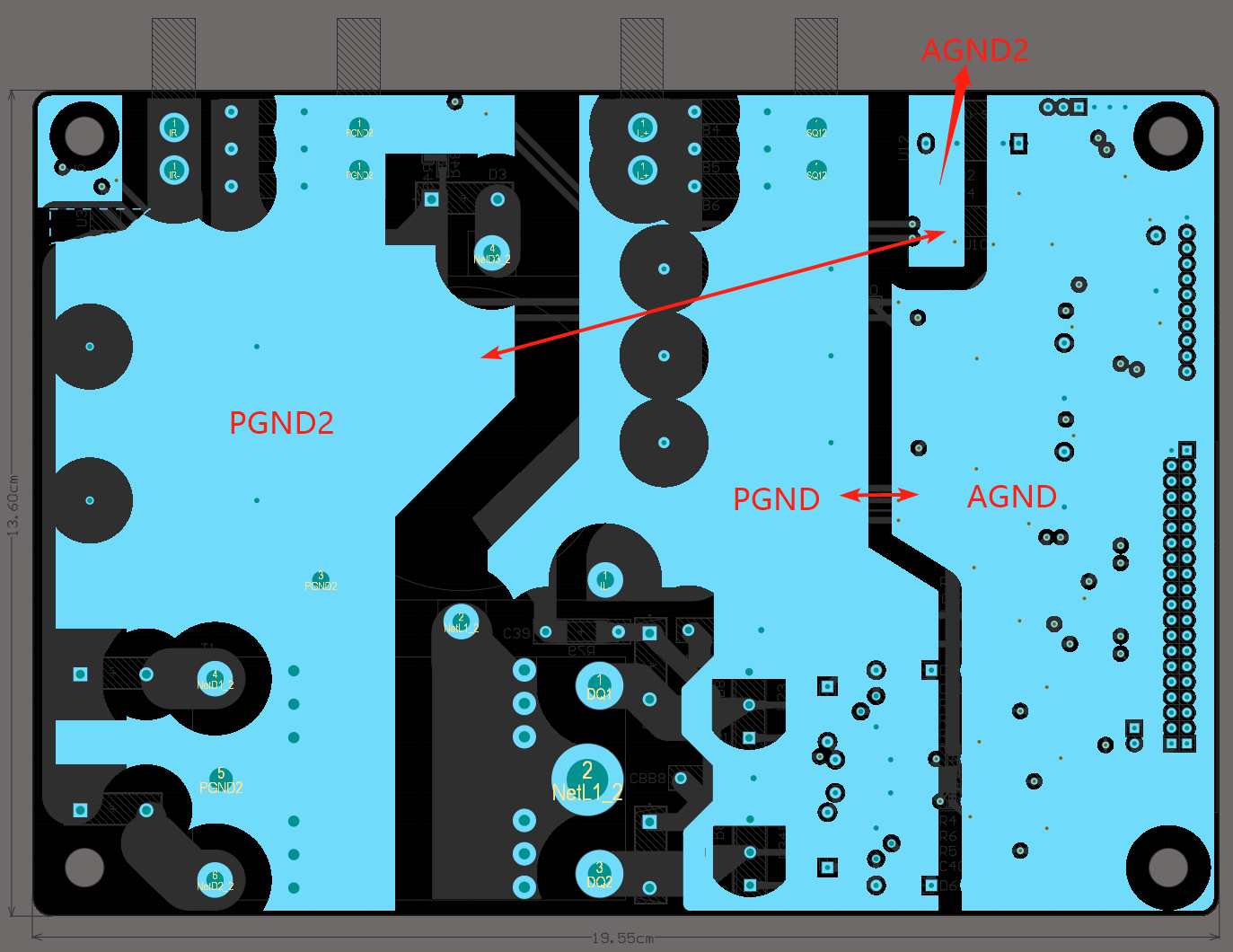

功率地与信号地

菜鸟曾经搞不清如何接地。甚至忘记焊0Ω电阻,怎么调都不对劲。现在大概知道了。

不隔离的话,一般只有两个地,功率地(PGND)和信号地之间分开铺地,最后通过0Ω电阻相连。

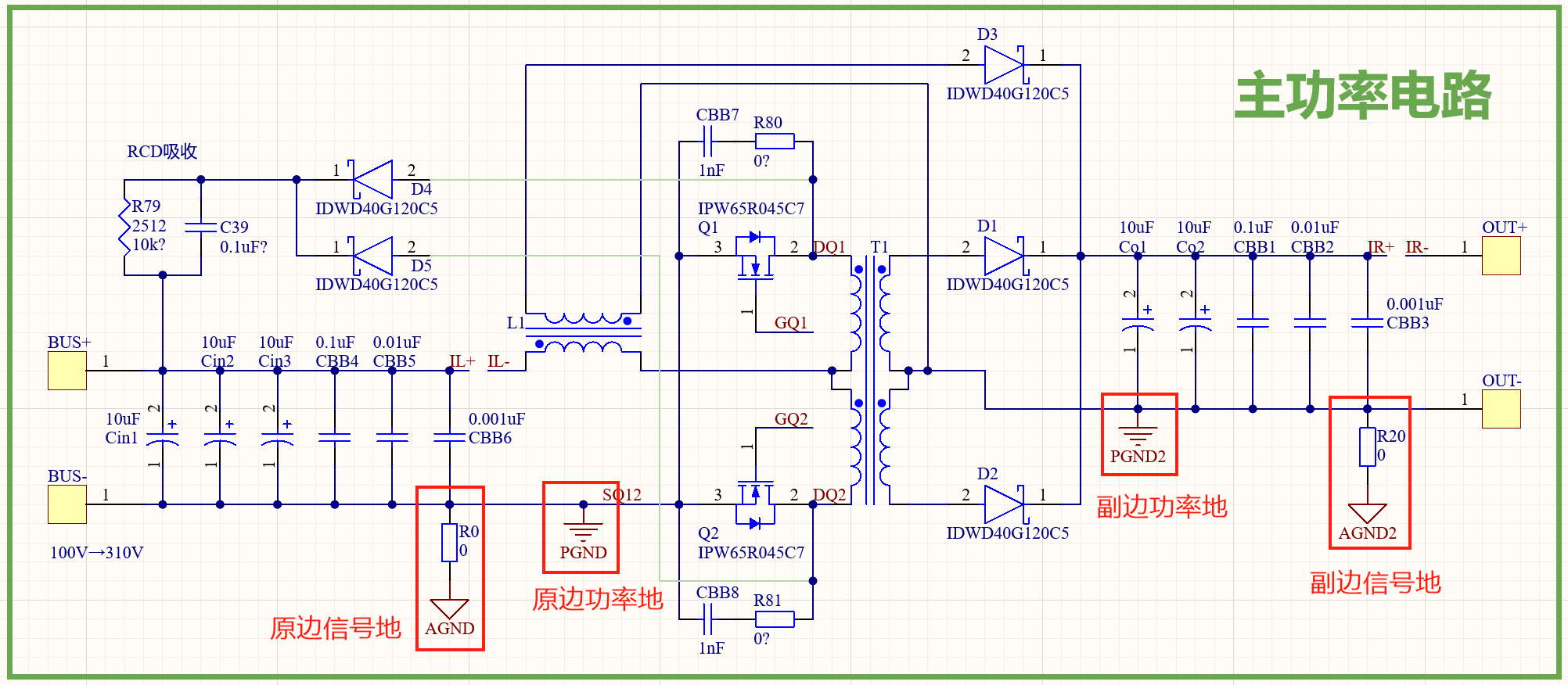

隔离的话,原边两个地,副边两个地,至少就有四个GND了,如下图,两边分别通过0Ω电阻相连。

有时候模拟地(AGND)和数字地(DGND)也会分开,但最终也是要连在一起的。

总而言之,分开的是路径,连接的是电位。殊途同归。同归于零。

至于控制回路应该和原边共地还是副边共地,怎么方便怎么来。

铺铜

铺铜不是GND的专利哦,有些粗的功率线也可以用铺铜的方式来画。可以理解为画图中的油漆桶工具。

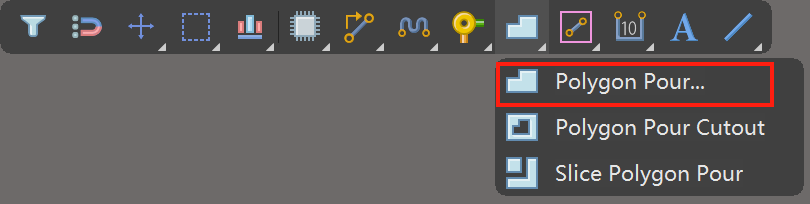

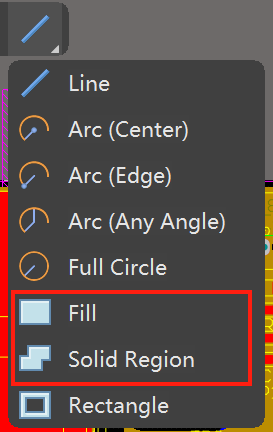

一共有三个工具涉及铺铜,工具条里的Polygon Pour是智能铺铜,有避障功能的,还有一个Fill是绘制方块铜皮,Solid Region是绘制多边形铜皮。选中区域重新铺铜的快捷键是TGR。

一般GND是单独铺整层,因为连接GND的节点很多,毕竟很多模块都需要零电位参考嘛,电源负端也要连GND,所以这个节点是地下水源,很多地方都需要连它,那索性修到家家户户门口嘛,实在够不着打口井(过孔)就能接到地了。

理论上凡是电位稳定的节点都可以铺铜,因为铺铜还有一个附带的好处就是可以屏蔽干扰,但是大多数节点的电位肯定都不如零电位的GND那么稳定,所以铺地是最常见的,其他节点的铺铜就比较少见,除非是为了拓宽走线面积。

快捷键

Ctrl+W 连线

Ctrl+M 测量(比放置尺寸好用)

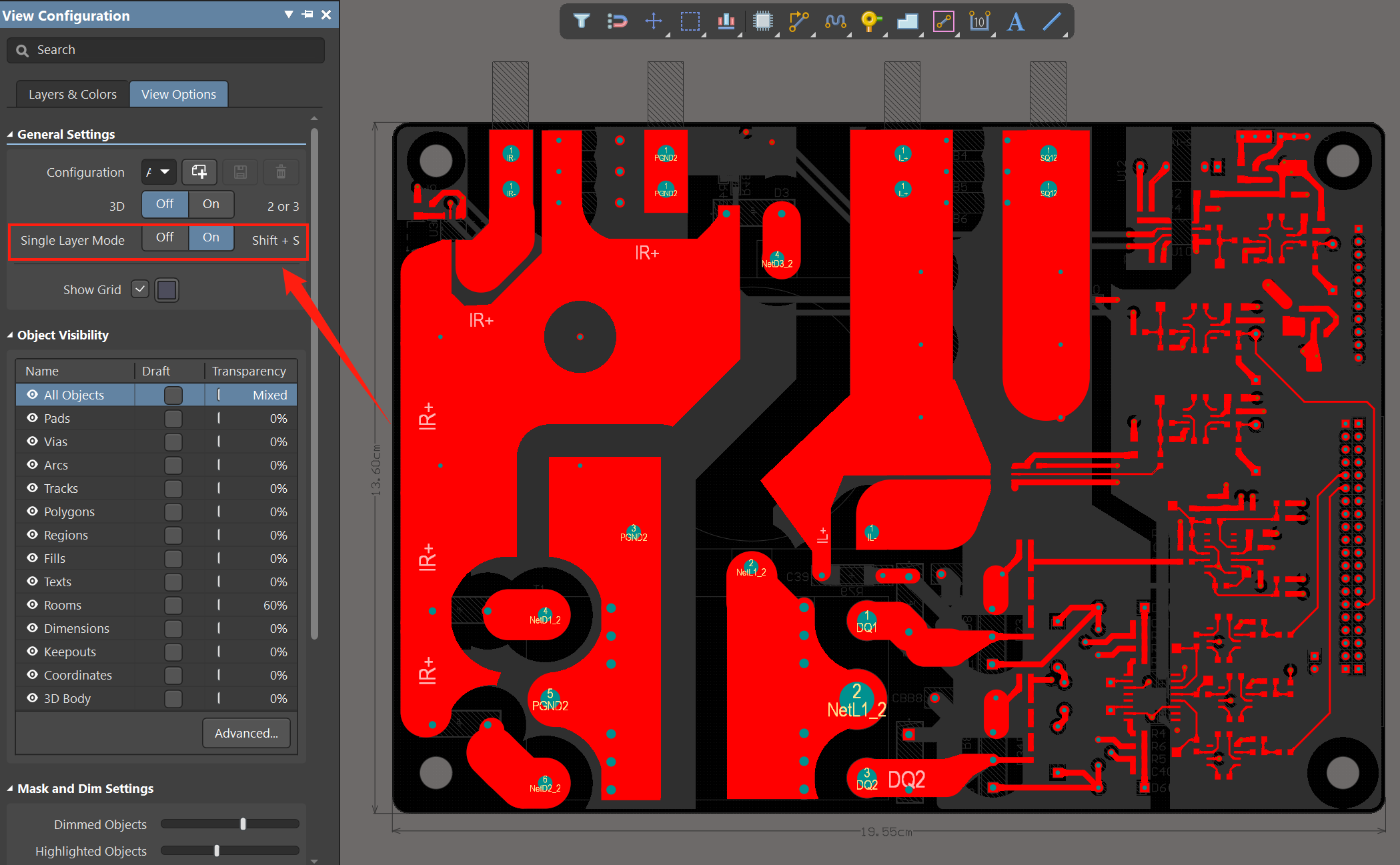

Shift+S 仅显示单层布线(比小眼睛图标好用)

元件布局

- SPACE 旋转

- X 水平翻转

- Y 垂直翻转

元件对齐(强迫症必会)

- Ctrl+Shift+L 左对齐

- Ctrl+Shift+R 右对齐

- Ctrl+Shift+T 上对齐

- Ctrl+Shift+B 下对齐

- Ctrl+Shift+H 水平均分

- Ctrl+Shift+V 垂直均分

字母键组合(菜单下划线字母)(英文输入法下)

- DR:Design-Rules 规则设置

- DC:Design-Classes 类别设置

- DK:Design-Layer Stack Manager 层管理器

- TGR:Tools-Polygon Pours-Repour Selected 选中部分重新铺铜

潜规则

- 滤波电容布局时靠近芯片引脚

- 驱动芯片布局时靠近MOS管

- MOS管靠近边缘排布有利于散热结构设计(但是不方便走线)

- 尽可能减小环路面积,比如U形回路

- 信号线夹在地层中间

- 强电、弱电分开布局

- 功率地、信号地、数字地、模拟地分开

- 放不下的元器件可以放反面

看起来很奥利给

我只会一丢丢咖喱创

PCB小白觉得很赞~ 嘉立创打板都不怎么会,233 :

嘉立创打板都不怎么会,233 :